KAPow: Wins best paper award at FCCM16, Washington DC.

PRiME researchers at Imperial College, London, have developed a modelling tool for FPGA designs which allows users to monitor the power consumed by individual modules in the design. The tool is called KAPow – a loose acronym for ‘K’ounting Activity for Power estimation.

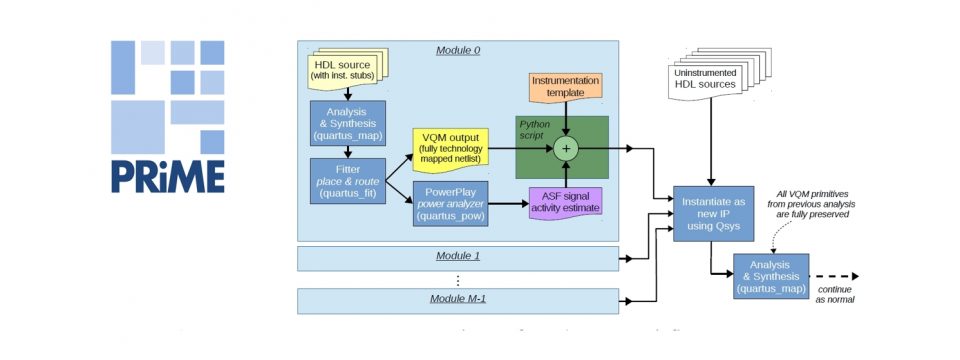

Modern Field Programmable Gate Arrays (FPGAs) can consist of highly complex system-on-chip designs, with significant system power consumption. It is often insufficient to simply assess the total power consumption of the whole circuit – either by estimations at the design phase or by power rail measurements on the final system. KAPow combines board level power measurements with register-level activity counting to build a low overhead online model that produces a breakdown of power consumption per module within the design. This per-module power estimation allows the system to determine an efficient mapping of tasks to modules, and using this approach has been shown to reduce system-wide power consumption by over 8% on an example application.

Prof. George Constantinides, deputy director of the PRiME research programme and research lead for PRiME theme 3 explained, “KAPow is all about trying to understand where your FPGA design is burning power, at run time, so that some higher level control entity can make intelligent decisions based on that information”.

PRiME’s work on KAPow was presented to the 24th IEEE International Symposium on Field-Programmable Custom Computing Machines, held on May 1-3 in Washington DC, USA (http://fccm.org/2016/) and was honoured to receive the prestigious Best Paper award in a very strong field.

The KAPow tool will shortly be made available as an open-source release via the PRiME web page.